Avicena introduced a new performance milestone for its microLED-based LightBundle optical interconnects at SuperCompute 2025, driving 4Gbps per lane at transmitter currents of just 100µA per LED. At this operating point, each link closes at a raw BER of 1×10-12 with energy usage of 80fJ/bit—achieved without Forward Error Correction. The company positioned the advancement as a step toward scalable, low-power interconnects required for memory disaggregation and multi-rack AI cluster architectures.

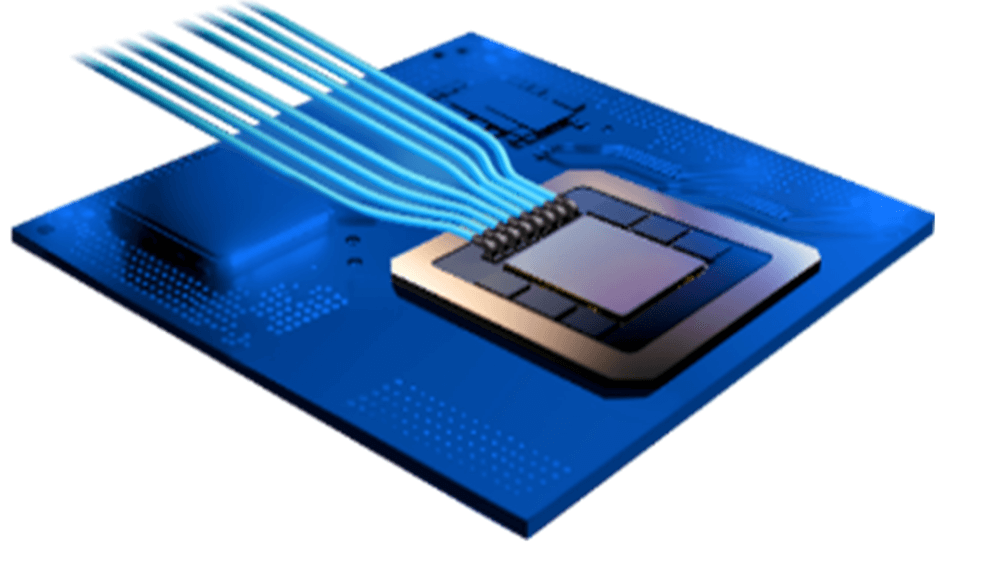

The LightBundle architecture avoids laser-based optical engines and instead uses microscopic, individually driven microLEDs that emit their own light, eliminating temperature stabilization, resonant modulators, and external laser distribution. In parallel with transmitter improvements, Avicena developed high-sensitivity receivers based on image-sensor-derived photodetectors manufactured with high-volume CMOS processes. These receivers enable operation at extremely low optical power while maintaining timing margin and link stability.

The platform sends raw parallel data rather than serializing lower-speed on-chip lanes into multi-tens-of-Gbps optical channels. Avicena said this approach reduces latency, simplifies I/O design, and allows very dense microLED arrays to scale to terabit-level aggregate bandwidth. LightBundle chiplets support on-board optics, pluggables, co-packaged optics, and wide memory interconnect topologies, with the company working alongside hyperscalers, accelerator vendors, and memory suppliers to support emerging agentic-AI workloads.

• microLED-based LightBundle links now reach 4Gbps/lane at 100µA per LED

• Achieves 80fJ/bit without FEC at raw BER of 1×10-12

• High-sensitivity receivers derived from image-sensor photodetector processes

• Parallel, low-latency optical I/O avoids high-speed serialization

• Supports CPO, OBO, pluggables, and memory-disaggregation chiplet architectures

• Targeted at multi-rack AI clusters, HPC systems, and future disaggregated compute designs

“We already demonstrated an efficient microLED link in a live demo at ECOC 2025,” said Rob Kalman, Chief Scientist at Avicena. “By further optimizing our highly sensitive receivers, we have managed to further reduce the operating currents of the microLEDs and obtained Tx energy consumption down further to tens of femtojoules… We can achieve unmatched energy efficiency in our LightBundle interconnects.”

🌐 Analysis: Avicena’s push into microLED optical I/O arrives as hyperscalers test memory disaggregation and rack-scale fabrics for next-generation AI training clusters. Competing approaches—from silicon-photonics modulators to integrated lasers and emerging co-packaged optics platforms—are chasing power reductions for multi-Tbps interconnects. Avicena’s self-emissive microLED model removes several complexity layers, but its adoption will hinge on manufacturing scalability and integration across AI accelerator and memory vendors.