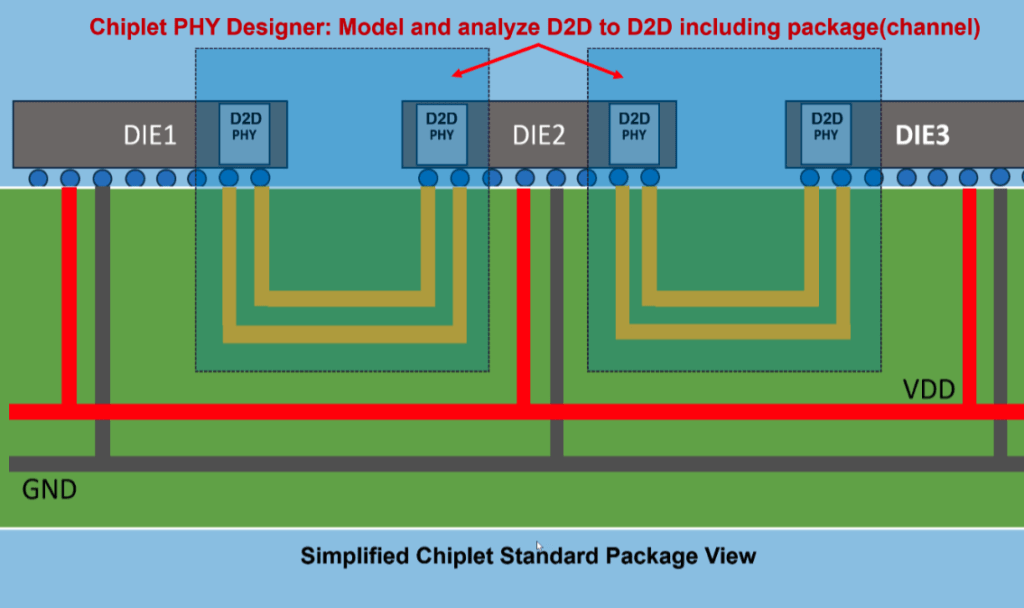

Keysight Technologies introduced Chiplet PHY Designer, a new tool for high-speed digital design and simulation. This tool focuses on die-to-die (D2D) interconnect simulation, which is crucial for verifying the performance of heterogeneous and 3D integrated circuit (IC) designs, commonly known as chiplets. It’s the industry’s first electronic design automation (EDA) tool that offers detailed modeling and simulation capabilities, enabling chiplet designers to verify that their designs meet the specifications of the Universal Chiplet Interconnect Express (UCIe) standard.

UCIe is becoming the leading chiplet interconnect specification in the semiconductor industry. It’s an open standard that defines interconnects between chiplets within advanced 2.5D or 3D packages. UCIe is gaining support from top semiconductor equipment and EDA tool vendors, foundries, and chiplet designers. Designers adopting this interconnect standard and ensuring their chiplets meet its specifications contribute to building a broad ecosystem for chiplet interoperability and commerce.

Keysight EDA’s R&D team has extensive experience in modeling and simulating high-speed digital interfaces aligned with industry standards. For example, ADS Memory Designer covers various memory interfaces like GDDR7, DDR5, LPDDR5, and HBM3 with its IBIS-AMI modeler. Additionally, its JEDEC compliance test solution handles over 100 test IDs using the same algorithm as the Keysight Infinium oscilloscope family.

Key features of the Chiplet PHY Designer physical-layer simulator include:

- Supports UCIe physical layer standard – automated parsing of signals following the standard naming conventions, automated connections between multiple dies through package interconnects, standard driven simulation setup such as speed grade, and intuitive measurement setup through specialized probe component.

- Measurement of voltage transfer function (VTF) – precisely computes a VTF to ensure UCIe specification compliance and analyzes system bit error rate (BER) down to 1e-27 or 1e-32 levels.

- Measures eye diagram height, eye width, skew, mask margin, and BER contour.

- Analysis of forwarded clocking to accurately capture the asynchronous clocking behavior.