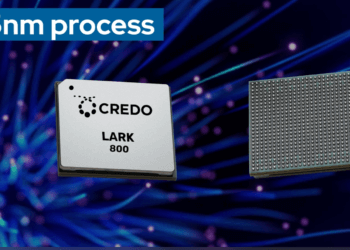

Credo Technology has unveiled its 224G PAM4 SerDes IP on TSMC’s N3 process technology, a major step toward enabling 1.6Tbps network connectivity for AI, cloud, and hyperscale data center workloads. The new offering doubles the data rate of its 112G predecessor while targeting improved energy efficiency and reliability. Fabricated on TSMC’s advanced 3nm process, the IP aims to give chipmakers a foundation for building custom silicon optimized for next-generation infrastructure.

The SerDes IP supports 224G per lane transmission, a speed tier seen as essential for upcoming 1.6Tbps port connectivity deployments. This performance is expected to play a pivotal role in scaling compute-intensive AI workloads and cloud applications. Market analysts project the 1.6Tbps networking segment will grow to $13 billion by 2028, with initial ramp starting later this year.

Credo’s full SerDes portfolio spans 28G to 224G and offers signaling across multiple reach options—very short reach plus (VSR), medium reach (MR), long reach (LR), and long reach plus (LR+). The company backs its IP with evaluation boards, simulation models, characterization reports, and supporting documentation to accelerate customer adoption.

- 224G PAM4 doubles the data rate of 112G predecessors

- Targets 1.6Tbps port connectivity for AI and hyperscale applications

- Fabricated on TSMC’s N3 advanced process node

- Market for 1.6Tbps networking projected at $13B by 2028

- Portfolio spans 28G to 224G across multiple reach options

“Credo’s 224G PAM4 IP doubles the data rate of our 112G PAM4 IP predecessor to help our customers ramp quickly and efficiently design cutting-edge connectivity solutions at 1.6T network speeds,” said Jeff Twombly, Vice President of Business Development at Credo.

🌐 Analysis

The introduction of 224G PAM4 SerDes marks a critical milestone in the evolution of high-speed interconnects. Over the past decade, SerDes speeds have advanced from 25G NRZ to 56G PAM4, then to 112G PAM4, which underpins today’s 800G and 1.6T Ethernet deployments. The jump to 224G PAM4 doubles lane throughput, enabling the transition to 1.6T and paving the way for 3.2T port architectures. Beyond 224G, the roadmap points toward 448G per lane, which will be required to sustain future 3.2T and 6.4T interfaces as hyperscale and AI clusters continue to grow.

At these higher speeds, modulation challenges intensify. PAM4, which encodes two bits per symbol across four voltage levels, already requires sophisticated DSP, equalization, and FEC at 112G. Moving to 224G heightens issues such as channel loss, jitter, crosstalk, and non-linearities, while leaving narrower voltage margins and higher susceptibility to noise. Looking ahead to 448G, the industry may need to transition to higher-order modulation such as PAM6 or PAM8, or explore alternative signaling schemes coupled with advanced packaging and clock recovery solutions.

Credo’s implementation of 224G PAM4 on TSMC’s 3nm node highlights the critical role of advanced silicon processes in delivering power efficiency and density at scale. This generation is expected to serve as the bridge between the 112G era and the experimental 448G phase, testing the limits of modulation formats and packaging technologies for next-generation Ethernet and AI interconnects.

We’re launching the “Data Center Networking for AI” series on NextGenInfra.io and inviting companies building real solutions—silicon, optics, fabrics, switches, software, orchestration—to share their views on video and in our expert report. To get involved, send a note to jcarroll@convergedigest.com or info@nextgeninfra.io.