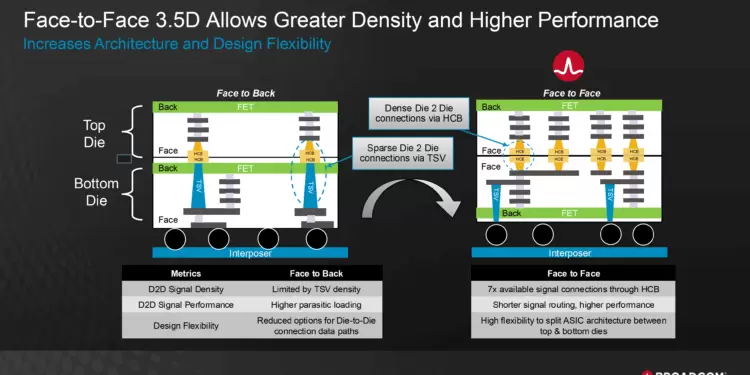

Broadcom has announced its 3.5D eXtreme Dimension System in Package (XDSiP) platform, a new technology designed for next-generation AI accelerators (XPUs). The platform integrates over 6,000 mm² of silicon and up to 12 high-bandwidth memory (HBM) stacks in a single package, enabling improved performance, reduced power consumption, and lower costs for AI at scale. The solution uses Broadcom’s Face-to-Face (F2F) 3.5D integration, combining 3D silicon stacking with 2.5D packaging, achieving denser, more efficient compute platforms.

The technology addresses the computational demands of generative AI model training, which require large clusters of up to 1 million XPUs. Traditional scaling methods struggle to keep up with performance requirements, making advanced system-in-package (SiP) integration a critical innovation. Broadcom’s 3.5D platform delivers key benefits such as higher interconnect density and power efficiency, leveraging 3D stacking to reduce latency and enhance integration. This advancement builds on the successes of 2.5D integration while incorporating vertical stacking to better handle the complexities of AI workloads.

Broadcom’s F2F stacking directly connects the top metal layers of adjacent dies, creating a high-density, low-interference interface. This configuration supports a compact form factor and high mechanical strength. Initial implementations combine compute dies, I/O dies, and HBM modules using TSMC’s advanced processes and CoWoS® packaging technologies. Broadcom’s custom design flow has enabled first-pass success for this platform, which will see commercial production beginning in February 2026.

• Enhanced Interconnect Density: 7x increase in signal density compared to Face-to-Back (F2B) stacking.

• Improved Power Efficiency: 10x reduction in power consumption for die-to-die interfaces.

• Reduced Latency: Faster interactions between compute, memory, and I/O components.

• Smaller Form Factor: Cost and size reductions via a more compact package design.

“Advanced packaging is critical for next-generation XPU clusters as we hit the limits of Moore’s Law,” said Frank Ostojic, Senior Vice President and General Manager, ASIC Products Division, Broadcom. “By stacking components vertically, our 3.5D platform allows designers to optimize fabrication processes and achieve significant improvements in performance, efficiency, and cost.”