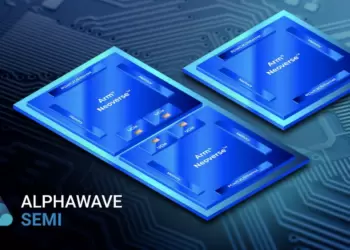

Alphawave Semi announced the availability of its 3nm silicon-proven Universal Chiplet Interconnect Express (UCIe) Die-to-Die (D2D) IP subsystem. Built on TSMC’s advanced Chip-on-Wafer-on-Substrate (CoWoS) packaging technology, this subsystem is designed for high-performance applications like hyperscale data centers, AI, and high-performance computing (HPC). The subsystem integrates both PHY and controller and provides up to 8 Tbps/mm of bandwidth density, while improving power efficiency, latency, and I/O complexity.

The UCIe IP subsystem supports multiple industry protocols including PCIe, CXL, AXI-4, AXI-S, CXS, and CHI, ensuring it fits within the evolving chiplet ecosystem. It operates at speeds of up to 24 Gbps and offers live per-lane health monitoring to enhance system robustness. Alphawave Semi has completed comprehensive testing on silicon received from TSMC, validating the subsystem’s performance under typical, slow, and fast conditions, and at different voltage and temperature ranges.

With full compliance to UCIe Specification Rev 2.0, the subsystem also includes JTAG, BIST, DFT, and Known Good Die (KGD) capabilities for testing and debugging. This release marks another step in Alphawave Semi’s strategic roadmap for delivering advanced connectivity solutions for next-generation semiconductor designs.

Key points:

• 3nm UCIe Die-to-Die IP subsystem now available.

• Built on TSMC’s Chip-on-Wafer-on-Substrate (CoWoS) advanced packaging.

• Bandwidth density of 8 Tbps/mm, supporting speeds up to 24 Gbps.

• Multiple protocol support: PCIe, CXL, AXI-4, AXI-S, CXS, and CHI.

• Includes JTAG, BIST, DFT, and Known Good Die (KGD) capabilities.

TSMC’s Chip-on-Wafer-on-Substrate (CoWoS) is a 3D stacked packaging solution that enables the integration of multiple chips, including CPUs, GPUs, memory, and other components, onto a single substrate.

“Achieving successful silicon validation of 3nm 24 Gbps UCIe subsystem with TSMC’s advanced packaging is a significant milestone for Alphawave Semi and underscores the company’s expertise in utilizing the TSMC 3DFabric™ ecosystem to deliver top-tier connectivity solutions,” said Mohit Gupta, Alphawave Semi’s SVP and GM, Custom Silicon and IP.