The U.S. Department of Energy’s (DOE) Argonne National Laboratory will spearhead two groundbreaking microelectronics research projects aimed at advancing hardware and software co-design for next-generation computing. Funded through the CHIPS and Science Act of 2022, these projects will support transformative breakthroughs in energy efficiency, data processing speed, and resilience under extreme conditions. Argonne will lead these initiatives as part of the DOE’s Microelectronics Science Research Centers, a $160 million investment announced in December 2024.

The two projects, titled “Ultra Dense Memory: Atom Scale Material Dynamics and Systems Consequences” and “BIA: A Co-Design Methodology to Transform Materials and Computer Architecture Research for Energy Efficiency”, will collaborate with leading academic and industry partners to push the boundaries of microelectronics design. The research will focus on developing next-generation memory architectures and methodologies for energy-efficient computing, supporting high-performance computing and advanced sensor technologies.

Key Highlights of the Argonne Microelectronics Projects:

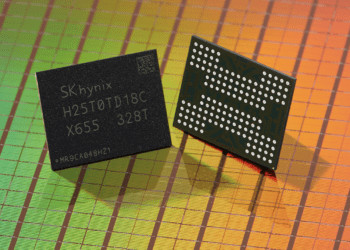

• Ultra Dense Memory Project:

• Led by Supratik Guha, senior adviser at Argonne.

• Focus: Developing extreme-scale memory for faster data processing.

• Partners: University of Chicago, Purdue University, Georgia Institute of Technology, Chicago State University.

• Industry Collaborators: IBM and Micron Technologies.

• BIA Project for Energy Efficiency:

• Led by Valerie Taylor, Distinguished Fellow and Director of Argonne’s Mathematics and Computer Science Division.

• Goal: Develop a co-design methodology for vertically stacked microelectronics, improving energy efficiency.

• Partners: Fermi National Accelerator Laboratory, University of Chicago, Northwestern University, Rice University.

• Industry Advisory Board: AMD, NVIDIA, Lam Research, Northrop Grumman, Enosemi.

These projects position Argonne at the forefront of microelectronics research, accelerating innovation in high-performance computing, AI, and sensor technologies while ensuring energy-efficient, scalable solutions for the next generation of information systems.