Cadence Design Systems introduced its deep neural-network accelerator (DNA) AI processor intellectual property for developers of articial intelligence semiconductors for use in applications spanning autonomous vehicles (AVs), ADAS, surveillance, robotics, drones, augmented reality (AR)/virtual reality (VR), smartphones, smart home and IoT.

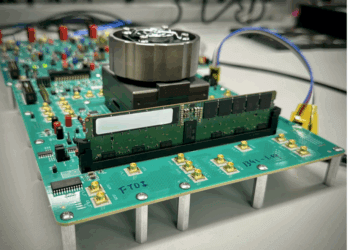

The Cadence Tensilica DNA 100 Processor IP targets high performance and power efficiency across a full range of compute from 0.5 TeraMAC (TMAC) to 100s of TMACs. The company said processors based on this IP could deliver up to 4.7X better performance and up to 2.3X more performance per watt compared to other solutions with similar multiplier-accumulator (MAC) array sizes. Compatibility with the latest version of the Tensilica Neural Network Compiler enables support for advanced AI frameworks including Caffe, TensorFlow, TensorFlow Lite, and a broad spectrum of neural networks including convolution and recurrent networks. This makes the DNA 100 processor an ideal candidate for on-device inferencing for vision, speech, radar, lidar and co

The Cadence Tensilica DNA 100 Processor IP targets high performance and power efficiency across a full range of compute from 0.5 TeraMAC (TMAC) to 100s of TMACs. The company said processors based on this IP could deliver up to 4.7X better performance and up to 2.3X more performance per watt compared to other solutions with similar multiplier-accumulator (MAC) array sizes. Compatibility with the latest version of the Tensilica Neural Network Compiler enables support for advanced AI frameworks including Caffe, TensorFlow, TensorFlow Lite, and a broad spectrum of neural networks including convolution and recurrent networks. This makes the DNA 100 processor an ideal candidate for on-device inferencing for vision, speech, radar, lidar and co

“The applications for AI processors are growing rapidly, but running the latest neural network models can strain available power budgets,” said Mike Demler, senior analyst at the Linley Group. “Meeting the demands for AI capabilities in devices ranging from small, battery-operated IoT sensors to self-driving cars will require more efficient architectures. The innovative sparse compute engine in Cadence’s new Tensilica DNA 100 processor addresses these limitations and packs a lot of performance for any power budget.”