Coherent Corp. has released a new 56 Gbaud PAM4 transimpedance amplifier (TIA), the CHR1065, targeting next-gen 400G and 800G optical transceivers for data center applications. The product is now in volume production and available as a wire-bondable bare die, with engineering samples shipping in 25-piece waffle packs.

Designed for DR, FR, and LR module designs, the CHR1065 delivers 2 µARMS input-referred noise for improved receiver sensitivity and extended optical reach. It also supports linearity up to 2.5 mA and operates at 227 mW per channel, balancing performance with power efficiency. System designers benefit from its 750 µm optical pitch, I2C-based advanced monitoring, and streamlined four-device integration, making it suitable for compact, high-density transceiver architectures in power-constrained environments.

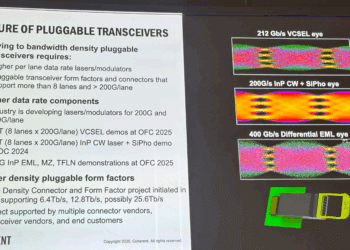

Coherent is positioning the CHR1065 as the newest entry in its open-market ASIC portfolio. “The CHR1065 is the latest example of this, soon to be followed by 112 GBaud ASICs and 224 GBaud thereafter,” said Dr. Beck Mason, Executive VP of Semiconductor Devices at Coherent.

• Targeted for 400G and 800G PAM4 optical transceivers

• 2 µARMS input-referred noise for enhanced reach and sensitivity

• 2.5 mA linearity and 227 mW/channel power draw

• I2C monitoring and 750 µm pitch for compact designs

• Fully released to volume production, with samples now available

🌐 Why it Matters: As hyperscalers push for higher-density, lower-power interconnects, Coherent’s expansion of its open-market ASIC offerings gives transceiver vendors a path to building differentiated modules while reducing time to market. With a roadmap toward 112 and 224 GBaud ASICs, Coherent is signaling long-term alignment with the accelerating pace of AI-era data center scaling.

🌐 We’re tracking the latest developments in networking silicon. Follow our ongoing coverage at: https://convergedigest.com/category/semiconductors/