Intel announced an integrated optical compute interconnect (OCI) chiplet co-packaged with an Intel CPU, representing a leap forward in high-bandwidth interconnect by enabling co-packaged optical input/output (I/O) in emerging AI infrastructure.

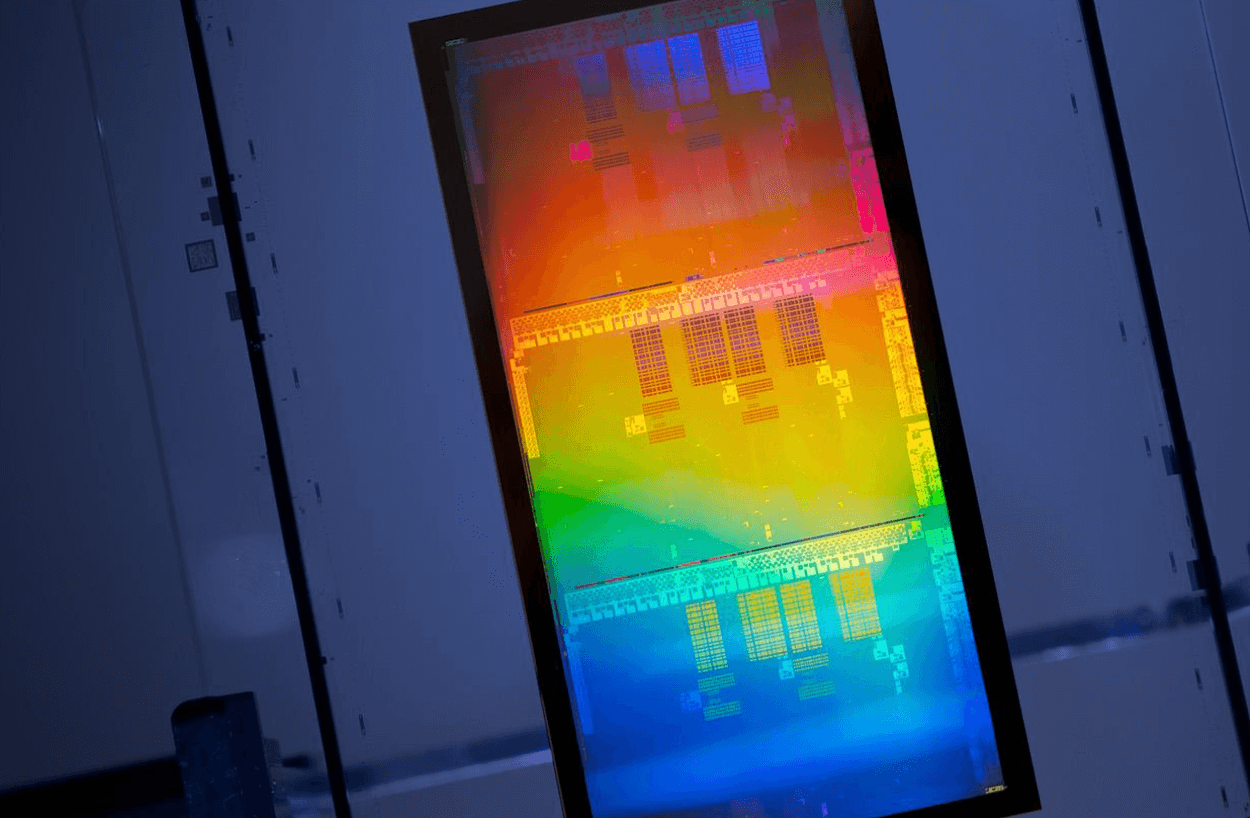

The prototype chiplet was demonstrated earlier this year at OFC 2024 (see video below).

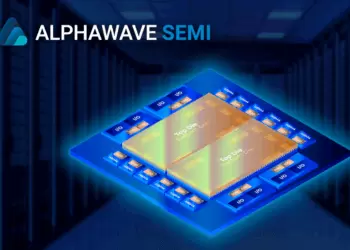

The fully Integrated OCI chiplet leverages Intel’s field-proven silicon photonics technology and integrates a silicon photonics integrated circuit (PIC), which includes on-chip lasers and optical amplifiers, with an electrical IC. The OCI chiplet demonstrated at OFC was co-packaged with an Intel CPU but can also be integrated with next-generation CPUs, GPUs, IPUs and other system-on-chips (SoCs).

This first OCI implementation supports up to 4 terabits per second (Tbps) bidirectional data transfer, compatible with peripheral component interconnect express (PCIe) Gen5. The live optical link demonstration showcases a transmitter (Tx) and receiver (Rx) connection between two CPU platforms over a single-mode fiber (SMF) patch cord. The CPUs generated and measured the optical Bit Error Rate (BER), and the demo showcases the Tx optical spectrum with 8 wavelengths at 200 gigahertz (GHz) spacing on a single fiber, along with a 32 Gbps Tx eye diagram illustrating strong signal quality.

The current chiplet supports 64 channels of 32 Gbps data in each direction up to 100 meters (though practical applications may be limited to tens of meters due to time-of-flight latency), utilizing eight fiber pairs, each carrying eight DWDM wavelengths. In terms of energy efficiency, the co-packaged solution consumes only 5 pico-Joules (pJ) per bit compared to pluggable optical transceiver modules at about 15 pJ/bit.

Key features of Intel’s OCI chiplet include:

- Fully integrated die stack, consisting of a single Intel® Silicon Photonics Integrated Circuit (PIC) with on-chip DWDM lasers and SOAs, and an advanced node CMOS electrical integrated circuit (EIC) with all the electronic devices required to form a complete optical I/O subsystem.

- No external laser source or optical amplification is required.

- The first-generation chiplet supports 4 Tbps bidirectionally, with a roadmap to tens of Terabits per second per device.

- Works over standard single-mode fiber (SMF-28).

- No polarization-maintaining fiber (PMF) is required.

- A path to incorporate a detachable optical connector.

- Designed to be co-packaged with next-generation CPU, GPU, IPU, and other SOCs.

- Stand-alone on-board implementations can also be supported.

- Chiplet-level evaluation platforms to be available.

- Based on the field-proven Intel Silicon Photonics platform, which has already shipped more than 8 million PICs with over 32 million on-chip lasers embedded in pluggable optical transceivers for data center networking, with industry-leading reliability.

“The ever-increasing movement of data from server to server is straining the capabilities of today’s data center infrastructure, and current solutions are rapidly approaching the practical limits of electrical I/O performance. However, Intel’s groundbreaking achievement empowers customers to seamlessly integrate co-packaged silicon photonics interconnect solutions into next-generation compute systems. Our OCI chiplet boosts bandwidth, reduces power consumption and increases reach, enabling ML workload acceleration that promises to revolutionize high-performance AI infrastructure,” stated Thomas Liljeberg, senior director, Product Management and Strategy, Integrated Photonics Solutions (IPS) Group.

https://www.intel.com/content/www/us/en/products/details/network-io/silicon-photonics.html