The U.S. Department of Defense awarded Intel an agreement to provide commercial foundry services in the first phase of its multi-phase Rapid Assured Microelectronics Prototypes – Commercial (RAMP-C) program.

The RAMP-C program was created to facilitate the use of a U.S.-based commercial semiconductor foundry ecosystem to fabricate the assured leading-edge custom and integrated circuits and commercial products required for critical Department of Defense systems. In October 2020, DOD launched the RAMP program using the Advanced Commercial Capabilities Project Phase 1 Other Transaction Authority.

The contract was awarded to the newly established Intel Foundry Services business through the NSTXL consortium-based S2MARTS OTA. Financial terms were not disclosed.

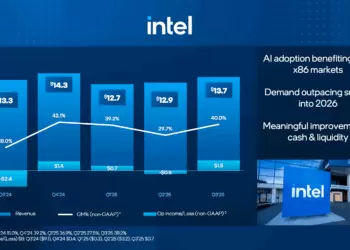

“One of the most profound lessons of the past year is the strategic importance of semiconductors, and the value to the United States of having a strong domestic semiconductor industry. Intel is the sole American company both designing and manufacturing logic semiconductors at the leading edge of technology. When we launched Intel Foundry Services earlier this year, we were excited to have the opportunity to make our capabilities available to a wider range of partners, including in the U.S. government, and it is great to see that potential being fulfilled through programs like RAMP-C,” stated Pat Gelsinger, Intel CEO

Under RAMP-C Intel Foundry Services will partner with industry leaders, including IBM, Cadence, Synopsys and others, to support the U.S. government’s needs for designing and manufacturing assured integrated circuits by establishing and demonstrating a semiconductor IP ecosystem to develop and fabricate test chips on Intel 18A, Intel’s most advanced process technology.

“The RAMP-C program will enable both commercial foundry customers and the Department of Defense to take advantage of Intel’s significant investments in leading-edge process technologies,” said Randhir Thakur, Intel Foundry Services president. “Along with our customers and ecosystem partners, including IBM, Cadence, Synopsys and others, we will help bolster the domestic semiconductor supply chain and ensure the United States maintains leadership in both R&D and advanced manufacturing. We look forward to a long-term collaboration with the U.S. government as we deliver RAMP-C program milestones.”

U.S. DoD backs Intel for semiconductor packaging tech

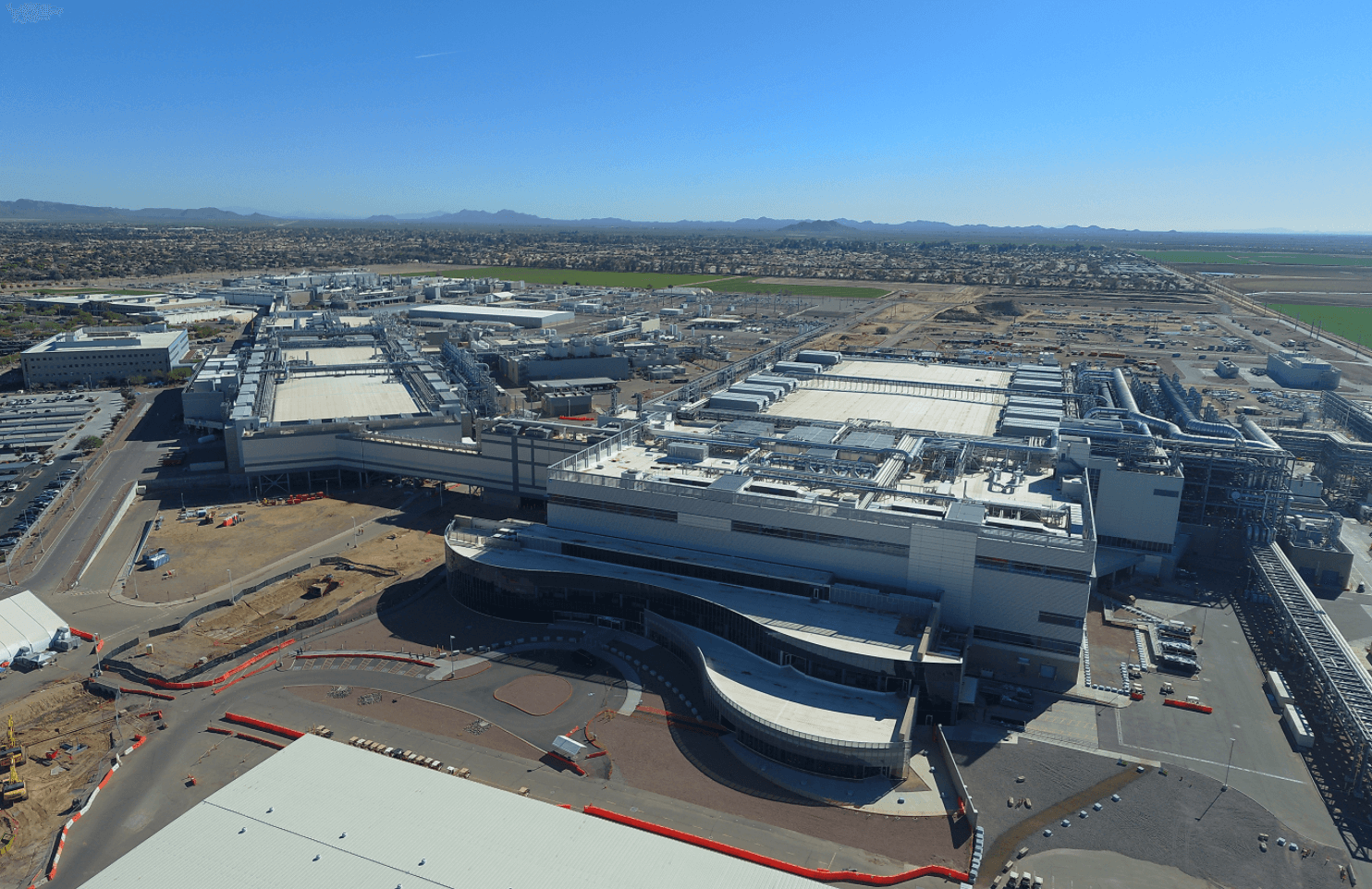

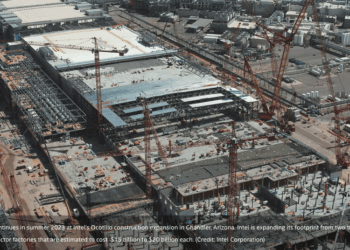

The U.S. Department of Defense awarded a contract to Intel to enable the U.S. government to access Intel’s state-of-the-art semiconductor packaging capabilities in Arizona and Oregon.

The project, which is supported by the DoD’s State-of-the-Art Heterogeneous Integration Prototype (SHIP) program, is executed by the Naval Surface Warfare Center, Crane Division, and administered by the National Security Technology Accelerator.

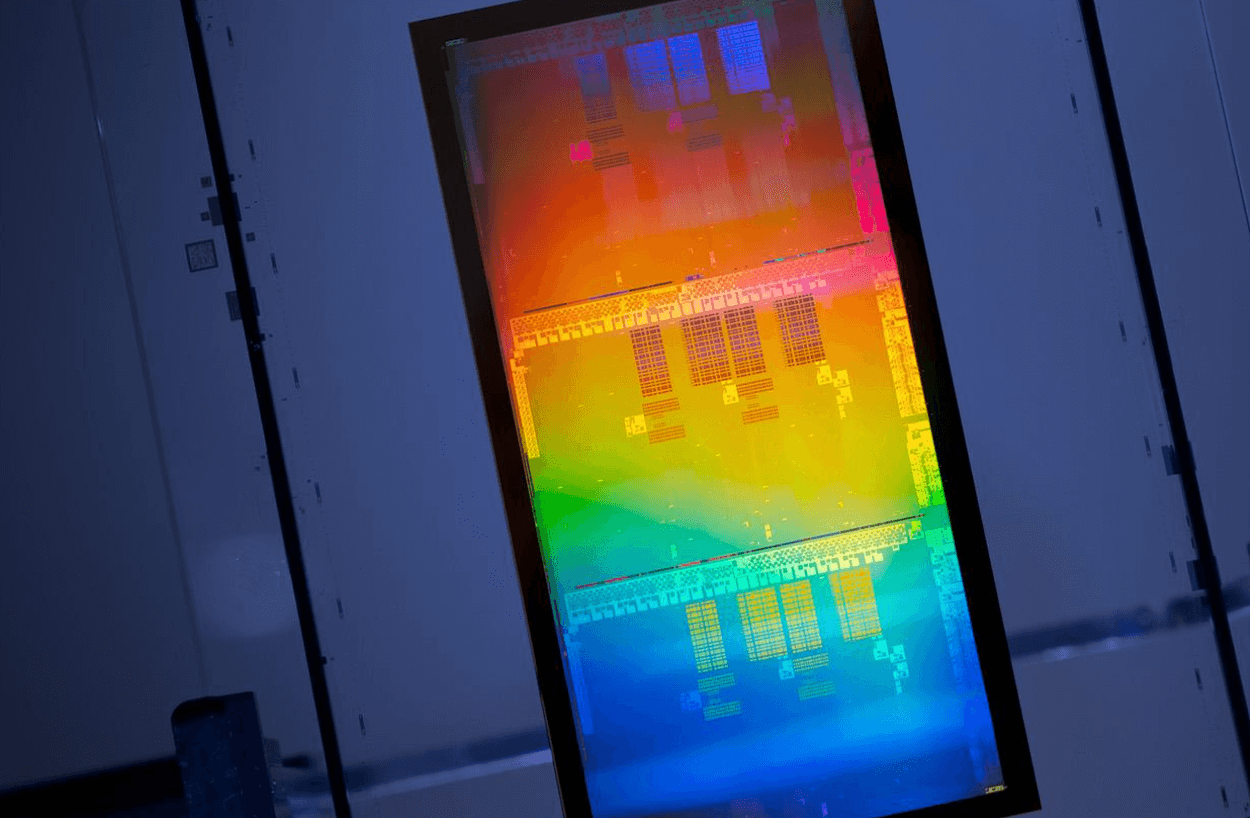

The second phase of SHIP will develop prototypes of multichip packages and accelerate advancement of interface standards, protocols and security for heterogeneous systems. SHIP prototypes will integrate special-purpose government chips with Intel’s advanced, commercially available silicon products, including field programmable gate arrays, application-specific integrated circuits and CPUs. This combination of technologies provides new paths for the U.S. government’s industry partners to develop and modernize the government’s mission-critical systems while taking advantage of Intel’s U.S. manufacturing capabilities.

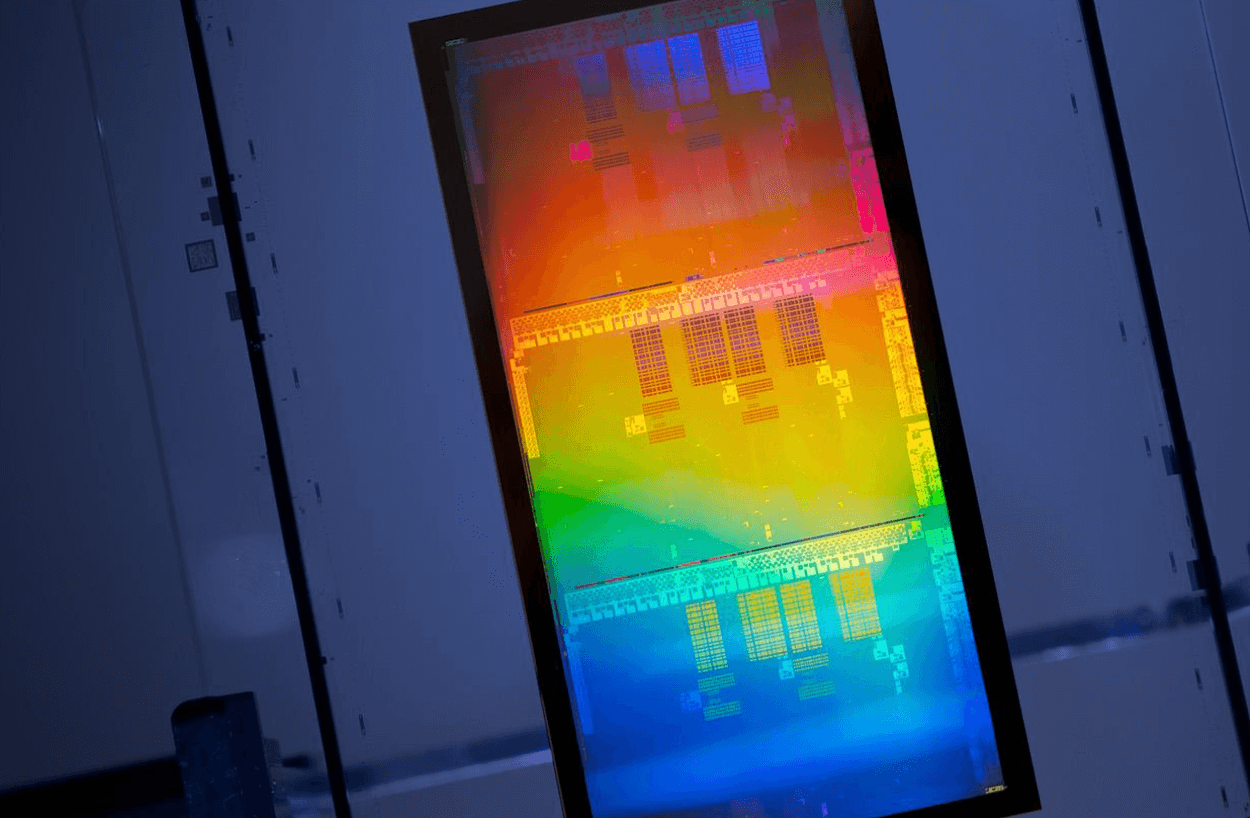

Heterogeneous packaging allows the assembly of multiple, separately manufactured integrated circuit dies (chips) onto a single package to increase performance while reducing power, size and weight. SHIP provides the U.S. government access to Intel’s advanced heterogeneous packaging technologies, including embedded multi-die interconnect bridge (EMIB), 3D Foveros and Co-EMIB (combining both EMIB and Foveros).

“Intel and the U.S. government share a priority to advance domestic semiconductor manufacturing technology. The SHIP program will enable the Department of Defense to take advantage of Intel’s advanced semiconductor packaging capabilities, diversifying their supply chain and protecting their intellectual property while also supporting ongoing semiconductor R&D in the U.S. and preserving critical capabilities onshore,” stated Jim Brinker, president and general manager of Intel Federal LLC.

“To ensure that the U.S. defense industry base can continue to deliver state-of-the-art electronics for national security, it is imperative that the Department of Defense (DoD) partners with leading U.S. semiconductor companies,” Nicole Petta, principal director of microelectronics, Office of the Under Secretary of Defense for Research and Engineering. “The DoD microelectronics roadmap recognizes the importance of strategic partnerships with industry. The roadmap also prioritizes and recognizes that as process scaling slows, heterogeneous assembly technology is a critical investment for both the DoD and our nation. SHIP directly contributes to advancing the objectives outlined in the DoD roadmap and the DoD looks forward to working with Intel, a world leader in this technology.”

In 2018, Intel demonstrated a new 3D packaging technology, called “Foveros,” which for the first time brings 3D stacking to logic-on-logic integration. Foveros will will allow products to be broken up into smaller “chiplets,” where I/O, SRAM and power delivery circuits can be fabricated in a base die and high-performance logic chiplets are stacked on top. The first Foveros product will combine a high-performance 10nm compute-stacked chiplet with a low-power 22FFL base die.