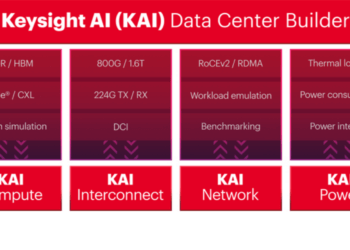

Keysight Technologies has introduced Chiplet PHY Designer 2025, its latest software solution for high-speed digital chiplet design tailored to AI and data center applications. The new release incorporates support for emerging chiplet interconnect standards, including Universal Chiplet Interconnect Express (UCIe) 2.0 and the Open Compute Project Bunch of Wires (BoW) standard, enabling engineers to validate designs for compliance in a system-level analysis environment. Chiplet PHY Designer streamlines pre-silicon validation for complex 2.5D and 3D package designs, accelerating the development process and minimizing risks associated with silicon re-spins.

The rise of AI and data center applications has driven the adoption of open chiplet interconnect standards like UCIe and BoW to ensure reliable communication between chiplets within advanced packages. Chiplet PHY Designer addresses these demands with new features such as Voltage Transfer Function (VTF) simulation, crosstalk analysis, and clocking scheme optimization for quarter-rate data rates (QDR). These tools allow engineers to model and verify designs for signal integrity, bit error rates (BER), and interoperability, ensuring compliance with industry standards while reducing time-to-market and development costs.

“Keysight EDA launched Chiplet PHY Designer one year ago as the industry’s first pre-silicon validation tool to provide in-depth modeling and simulation capabilities,” said Hee-Soo Lee, High-Speed Digital Segment Lead at Keysight. “The 2025 version keeps pace with evolving standards like UCIe 2.0 and BoW, offering advanced features that save time and avoid costly rework while ensuring designs meet performance requirements before manufacturing.”

• Standards Support: Fully integrates simulation for UCIe 2.0 and BoW standards for interoperability across advanced packaging ecosystems.

• Streamlined Workflows: Automates compliance testing setup, such as Voltage Transfer Function (VTF) and signal integrity analysis, for faster time-to-market.

• Advanced Design Tools: Enhances accuracy with features for bit error rate (BER) analysis, systematic crosstalk testing, and precise clock synchronization.

• Optimization Capabilities: Includes QDR clocking scheme support for high-speed interconnects in complex designs.

• Early Adoption Success: Alphawave Semi and other partners validate the tool’s ability to ensure seamless operation in 2.5D/3D chiplet solutions.