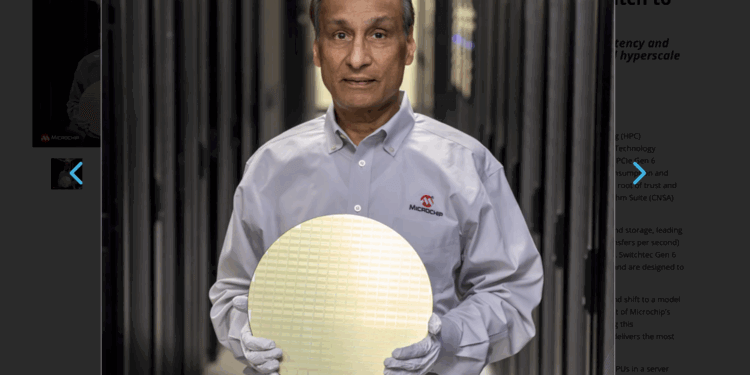

Microchip Technology has introduced its Switchtec Gen 6 PCIe switches, the industry’s first PCIe Gen 6 fanout switches built on a 3 nm process. Designed to meet the bandwidth and latency requirements of modern AI, HPC, and cloud infrastructures, the new devices deliver up to 160 lanes of PCIe 6.0 connectivity at 64 GT/s per lane—doubling the throughput of PCIe 5.0 while improving power efficiency and signal integrity.

The Switchtec Gen 6 family features advanced security capabilities, including a hardware root of trust, secure boot, and post-quantum-safe cryptography compliant with the U.S. Commercial National Security Algorithm Suite (CNSA) 2.0. The switches enable high-speed links among CPUs, GPUs, AI accelerators, and storage devices to prevent data transfer bottlenecks that can waste compute cycles. New protocol updates, such as Flow Control Unit (FLIT) mode and Forward Error Correction (FEC), further enhance reliability for AI workloads that rely on small, frequent data exchanges.

The 20-port, 10-stack switch architecture integrates an onboard MIPS processor, supports hot-plug capability, Non-Transparent Bridging (NTB), multicast for one-to-many data paths, and detailed diagnostics through Microchip’s ChipLink GUI tools. The PM61160-KIT evaluation platform and diagnostic suite enable developers to test and optimize connectivity designs quickly for hyperscale data center deployments. Sampling is now available for qualified customers.

• 3 nm process node with up to 160 PCIe 6.0 lanes at 64 GT/s

• Hardware root of trust and post-quantum-safe cryptography (CNSA 2.0 compliant)

• FLIT mode, dynamic resource allocation, and lightweight FEC for reduced latency

• 20 ports/10 stacks with x8 and x16 bifurcation options

• Integrated MIPS processor, NTB, multicast, and ChipLink diagnostics support

“By expanding our proven Switchtec product line to PCIe 6.0, we’re enabling this transformation with technology that facilitates direct communication between critical compute resources and delivers the most powerful and energy-efficient switch we’ve ever produced,” said Brian McCarson, corporate vice president of Microchip’s data center solutions business unit.

🌐 Analysis: Microchip’s entry into the PCIe 6.0 switch market underscores the growing need for ultra-low-latency interconnects in AI and HPC clusters. The use of 3 nm fabrication aligns it with the most advanced process technologies now being adopted by data center silicon suppliers. Competing PCIe 6.0 switch offerings are emerging from Broadcom and Microsemi divisions, while NVIDIA and AMD continue optimizing native interconnects through NVLink 5 and Infinity Fabric. Microchip’s approach positions it as a key supplier of flexible, standards-based connectivity for hyperscaler AI architectures.

🌐 We’re tracking the latest developments in networking silicon. Follow our ongoing coverage at: https://convergedigest.com/category/semiconductors/