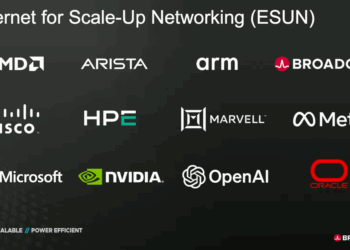

The Open Compute Project Foundation (OCP) announced major new contributions to its Open Chiplet Economy initiative, introducing the Foundation Chiplet System Architecture (FCSA) led by Arm and an enhanced BoW 2.0 chiplet interconnect led by Eliyan. These efforts aim to accelerate open, interoperable chiplet-based design for AI, HPC, and memory-intensive workloads, strengthening collaboration across the silicon design ecosystem.

Arm’s Foundation Chiplet System Architecture (FCSA) defines a vendor-neutral baseline for partitioning monolithic SoCs into interoperable chiplets spanning processors, accelerators, memory, and I/O. By providing a common framework for System-in-Package (SiP) designers, FCSA promotes reuse, interoperability, and flexibility across chip architectures, supporting the shift toward disaggregated silicon design. The contribution lays groundwork for a neutral, architecture-independent chiplet marketplace and aims to reduce fragmentation across the chiplet ecosystem.

Eliyan’s contribution extends the OCP Bunch of Wires (BoW) specification to version 2.0, enabling advanced memory connectivity for AI and HPC systems. The update adds bidirectional data support, configurable lane direction, expanded slice width for error correction, and tighter clock-data alignment. These enhancements target emerging HBM4 memory performance needs of up to 2 TB/s while fitting within a compact <10 mm die beachfront—addressing the “Memory Wall” that constrains AI and XPU performance.

• Arm leads the FCSA workstream, derived from its Chiplet System Architecture (CSA) and contributed under an open, vendor-neutral framework

• Eliyan leads the BoW 2.0 memory interconnect enhancement for high-bandwidth workloads including AI, HPC, gaming, and automotive

• The OCP Chiplet Marketplace launched in 2024 continues expanding, listing reusable chiplets, design tools, and services

• New specifications promote interoperability, tooling alignment, and scalable design approaches across silicon vendors

“These contributions reflect the momentum of the Open Chiplet Economy, as it is based on a strong foundation of collaboration on open standardizations, tools and best practices,” said Cliff Grossner, Ph.D., Chief Innovation Officer at OCP. “Together they mark an important step toward open, interoperable silicon systems for designing, building and deploying economically viable and dynamic AI clusters capable of achieving world-leading performance.”

🌐 Analysis: The Open Compute Project’s latest chiplet contributions reinforce its growing influence in silicon system design, paralleling broader industry trends toward open, multi-vendor chiplet ecosystems. Arm’s FCSA aligns with the industry’s push for modular SoC decomposition, while Eliyan’s BoW 2.0 work targets one of the toughest challenges—memory bandwidth at AI scale. These developments position OCP as a central coordination hub for disaggregated, standards-based chiplet innovation, complementing similar initiatives from UCIe Consortium, OpenHBI, and major foundry ecosystems.

🌐 We’re tracking the latest developments in networking silicon. Follow our ongoing coverage at: