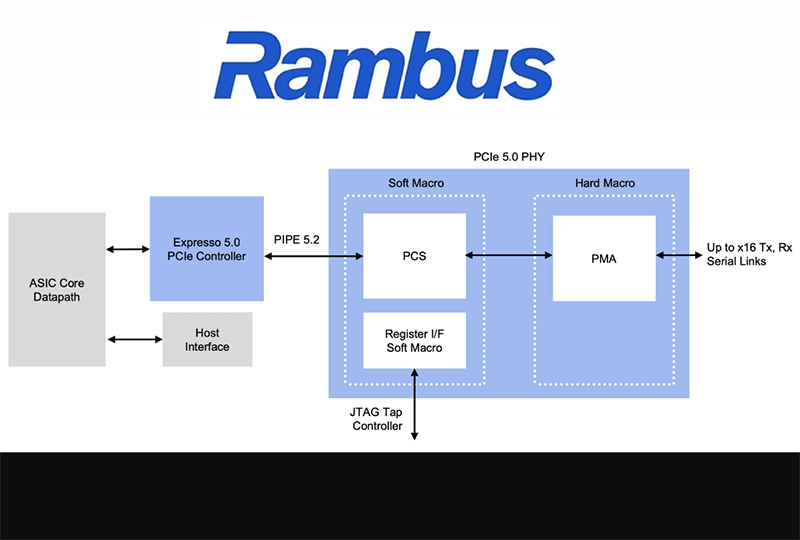

Rambus announced a comprehensive and optimized interface for PCI Express (PCIe) 5.0 in an advanced 7nm FinFET process, and offering backward compatibility to PCIe 4.0, 3.0 and 2.0.

The Rambus PCIe 5.0 interface solution includes both PHY and digital controller for easy SoC integration and faster time to market.

Highlights of Rambus PCIe 5.0 solution

- Integrated and co-validated PHY and digital controller for complete interface solution

- Built with Rambus’ industry-proven design methodology for long-reach PCIe interfaces

- 32 GT/s bandwidth per lane with 128 GB/s bandwidth in x16 configuration

- Backward compatible to PCIe 4.0, 3.0 and 2.0

- Supports Compute Express Link interconnect

- Advanced multi-tap transceiver and receiver equalization compensate for more than 36dB of insertion loss

“Our high-speed SerDes and memory interface solutions make possible amazing advancements in performance-intensive applications in AI, data center, HPC, storage and networking,” said Hemant Dhulla, vice president and general manager of IP cores at Rambus. “Now we’ve added PCIe 5 to our industry-leading portfolio of high-speed interface solutions giving chip makers another tool to unleash the power of their designs.”