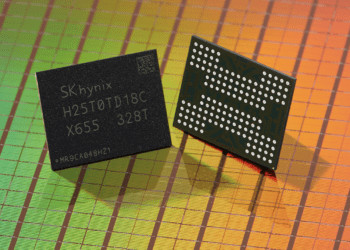

Rambus has begun sampling its 5600 MT/s 2nd-generation registering clock driver (RCD) chip to the major DDR5 memory module (RDIMM) suppliers.

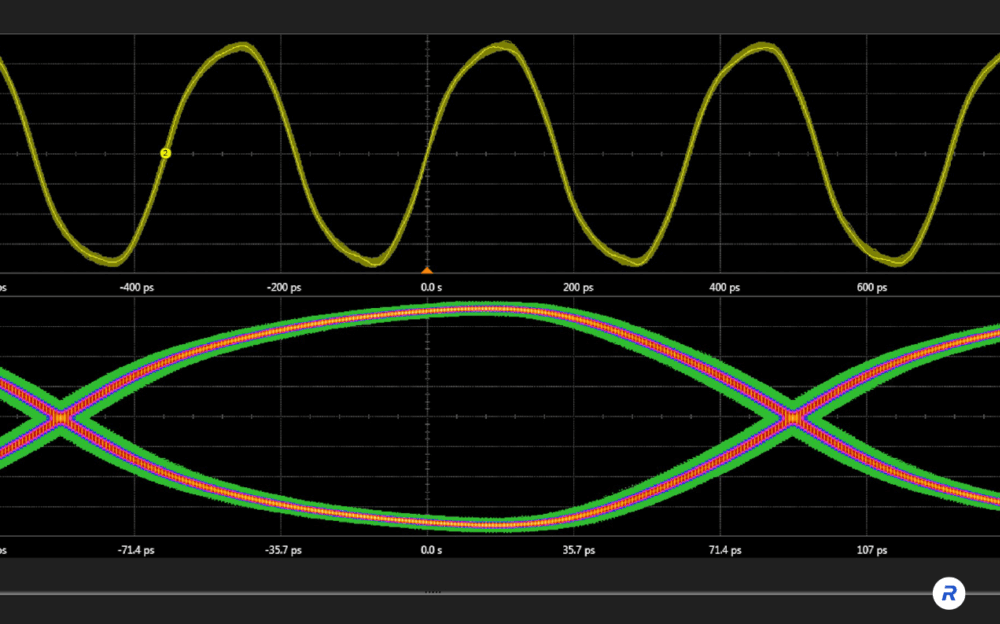

This new level of performance represents a 17% increase in data rate over the first-generation 4800 MT/s Rambus DDR5 RCD.

Rambus said it is able to deliver 5600 MT/s performance at lower latency and power while optimizing timing parameters for improved RDIMM margins.

“The RCD is a mission-critical enabler of DDR5 server DIMMs that provide the bandwidth and capacity needed in next-generation data centers,” said Sean Fan, chief operating officer at Rambus. “Achieving the 5600 MT/s data rate is the latest demonstration of our continued leadership in DDR5 memory interface products.”