STMicroelectronics unveiled an innovative on-chip interconnect technology aimed at future system-on-chip (SoC) designs. The new technology, called STNoC (ST Network on Chip), builds on ST’s existing on-chip communications expertise while adding radical innovation derived from its research in Network-on-Chip (NoC) technologies.

ST expects NoC architecture will play a major role in improving design productivity. The innovative interconnection topology, called “Spidergon, will link the many intellectual propoerty (IP) blocks that make up a SoC device. Typically, these include one or more high performance processor cores as well as complex, dedicated IP blocks such as audio/video codecs, a wide range of connectivity IPs (USB, Ethernet, serial ATA, DVB-H, HDMI etc), and memories. Up till now, the interconnection between these blocks has been implemented via traditional circuit-switched buses but it has been widely accepted in recent years that a new interconnection methodology is required to develop SoC devices that contain a billion or more transistors organised in tens or even hundreds of IP blocks.

ST said traditional on-chip bus architectures are becoming a bottleneck. In the long term, techniques such as optical intra-chip communications, in which ST has already reported world-leading R&D results, may eliminate this problem. In the medium term, new intra-chip interconnection technologies will be required to maintain the combination of price/performance/power improvements required by customers.

NoC technology replaces the traditional circuit-switched bus by a packet-based paradigm incorporating a layered protocol stack analogous to a very simplified version of the networking paradigm. In this scenario, proven IP such as processor cores, cache memories, connectivity I/O functions, or specialized IP blocks such as audio/video codecs are simply plucked from a library, added to the SoC design and communicate with each other via a high-speed, low-power, small silicon area, packet-based communications protocol.

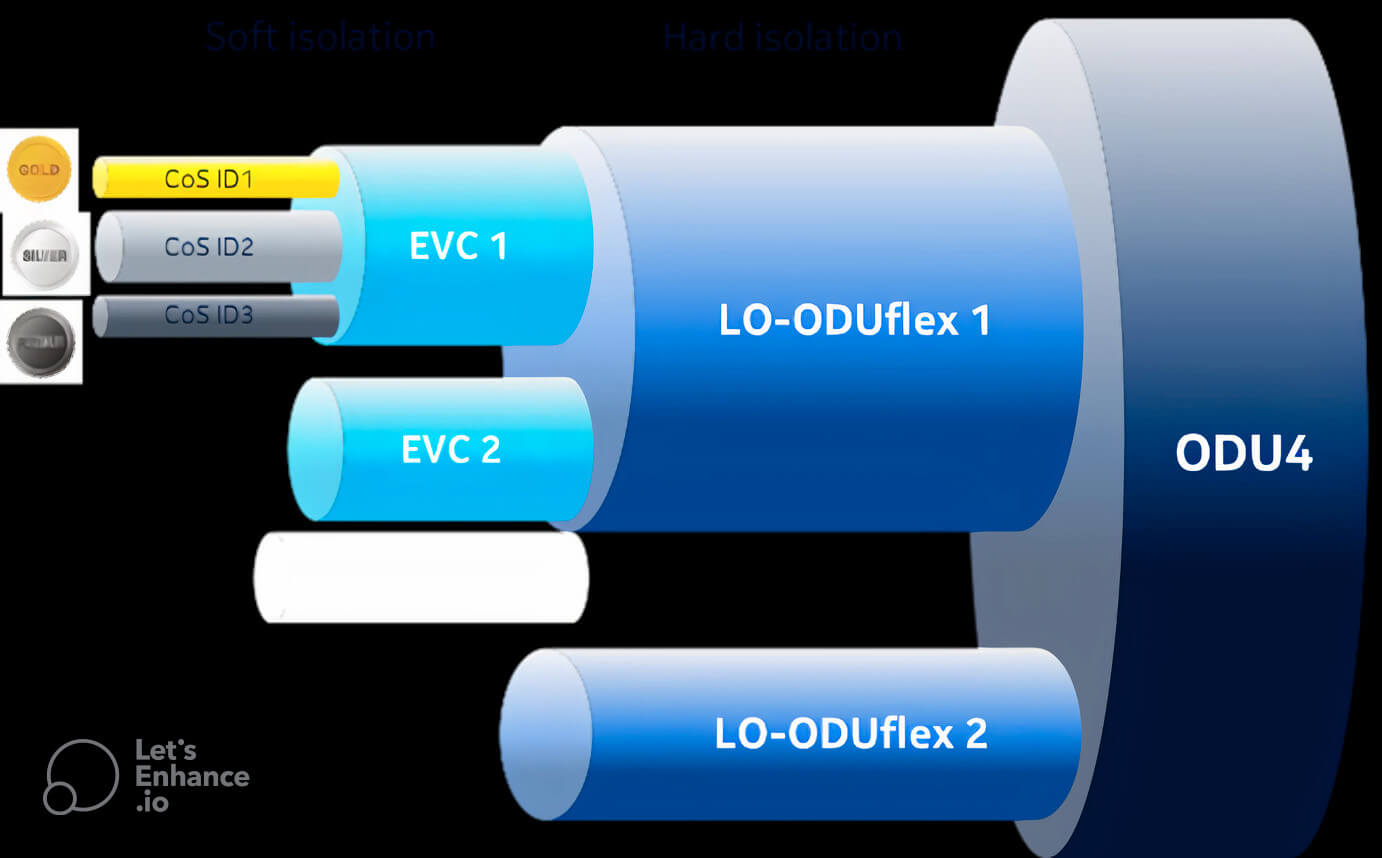

In the Spidergon topology, all of the IP blocks are arranged in a ring and each IP block is connected to its clockwise and its counter-clockwise neighbour as in a simple polygonal ring topology. In addition, however, each IP block is also connected directly to its diagonal counterpart in the network, which allows the routing algorithm to minimise the number of nodes that a data packet has to traverse before reaching its destination. A particularly important benefit is that the functional diagram for a network of 16 connected nodes shown on the left of the image corresponds to a simple planar implementation shown on the right in which the wiring only needs to cross itself at one point. This is a key benefit in translating theoretical approaches into actual solutions that deliver the maximum price/performance benefits.

http://www.st.com/stonline/press/news/year2005/t1741t.htm