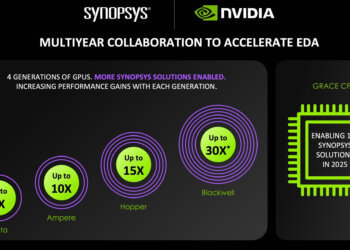

Synopsys, describing itself as the Silicon to Software partner for companies developing electronic products and software applications, announced its new DesignWare Multi-Protocol 25 Gbit/s PHY IP targeting high-performance computing applications including machine learning and artificial intelligence.

Synopsys’ new PHY IP allows designers to integrate multiple protocols including PCI Express 4.0, 25 Gigabit Ethernet, SATA and CCIX into system-on-chips (SoCs) targeting the 7 nm and 16 nm FinFET processes. The multi-protocol 25 Gbit/s PHY is claimed to reduce power and area requirements by over 35% compared to the 16 Gbit/s PHY solution via optional power management features such as I/O supply under drive and decision feedback equalisation (DFE) bypass.

In addition, the solutions features programmable continuous calibration and adoption (CCA), which is designed to optimise performance across voltage and temperature variations, which is key for applications in harsh data centre environments.

Designers are able to integrate the multi-protocol 25 Gbit/s PHY with Synopsys’ digital controllers and verification IP to provide a complete, low latency IP solution that is compliant with the industry-standard protocol specifications.

The new DesignWare multi-protocol 25 Gbit/s PHY IP offers designers key features including:

1. Flexible clock multiplier unit (CMU) with dual PLLs and dividers to support flexible multi-protocol configurations while transmitting data across lossy channels.

2. Analogue front-end that incorporates adaptive continuous time linear equaliser (CTLE), decision feedback equalisation (DFE) and feed forward equalisation (FFE) for enhanced signal integrity and jitter performance.

3. Embedded bit error rate (BER) circuitry for evaluating channel quality and on-die test features for testability and visibility into system performance without the need for external test equipment.

3. Embedded bit error rate (BER) circuitry for evaluating channel quality and on-die test features for testability and visibility into system performance without the need for external test equipment.

Synopsys noted that the silicon design kit for DesignWare multi-protocol 25 Gbit/s PHY IP for TSMC 7 nm FinFET process is currently available; the silicon design kit for TSMC’s 16 nm FinFET process is scheduled to be available in October.

The Synopsys DesignWare IP portfolio includes logic libraries, embedded memories, embedded test, analogue IP, wired and wireless interface IP, security IP, embedded processors and subsystems.