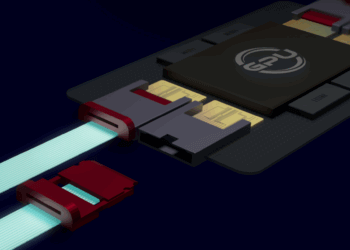

Tower Semiconductor introduced a new 3D-IC foundry capability that integrates its Silicon Photonics (SiPho) and SiGe BiCMOS electronic IC (EIC) processes at the wafer level, positioning the company to support emerging Co-Packaged Optics (CPO) designs. The technology adapts Tower’s high-volume 300mm wafer bonding platform—originally developed for stacked backside-illuminated image sensors—to serve data center and optical interconnect markets that require tightly coupled photonic and electronic functions.

The platform enables wafer-scale stacking of heterogeneous die, such as SiPho PICs and SiGe EICs, into dense 3D assemblies for high-performance optical subsystems. Tower said the combined wafer-bonding, precision alignment, and multi-PDK workflow allows customers to build smaller, higher-function devices for CPO and related optical modules. The 3D-IC capability is fully supported in Cadence’s Virtuoso Studio Heterogeneous Integration flow, enabling unified layout, checking, and simulation across stacked technologies.

Tower has demonstrated reliable process alignment across its 300mm lines and confirmed that customers can now access a complete reference design methodology developed with Cadence. The unified design flow supports die-to-wafer and wafer-to-wafer integration and is compatible with Tower’s SiGe and SiPho PDKs.

• 300mm wafer-scale 3D-IC integration now extended from CIS to SiPho + SiGe

• Supports Co-Packaged Optics (CPO) and PIC/EIC subsystem designs for data centers

• Unified Cadence design flow enables multi-technology co-simulation and verification

• Precision bonding demonstrated for wafer-to-wafer and die-to-wafer workflows

• Multi-PDK design environment supports first-pass silicon for stacked photonic-electronic ICs

“Our long-standing experience in high-volume wafer stacking for CIS technologies has laid the foundation for this next stage of 3D integration,” said Dr. Marco Racanelli, President, Tower Semiconductor.

🌐 Analysis

This move strengthens Tower’s positioning in the fast-emerging ecosystem around Co-Packaged Optics and wafer-scale heterogenous integration, an area gaining traction as AI data centers push for higher bandwidth density and tighter coupling between photonic I/O and near-package electronics. By aligning with Cadence on a unified 3D-IC flow, Tower joins a growing list of foundries offering design-ready heterogeneous integration for PIC/EIC systems, complementing efforts from Intel, GlobalFoundries, and TSMC as data-center optical roadmaps shift toward 200G/lane and 1.6T–3.2T modules.Tower Semiconductor introduced a new 3D-IC foundry capability that integrates its Silicon Photonics (SiPho) and SiGe BiCMOS electronic IC (EIC) processes at the wafer level, positioning the company to support emerging Co-Packaged Optics (CPO) designs. The technology adapts Tower’s high-volume 300mm wafer bonding platform—originally developed for stacked backside-illuminated image sensors—to serve data center and optical interconnect markets that require tightly coupled photonic and electronic functions.