Xilinx announced first customer shipment of its Virtex UltraScale+ FPGA, the industry’s first high-end FinFET FPGA built using TSMC’s 16FF+ process.

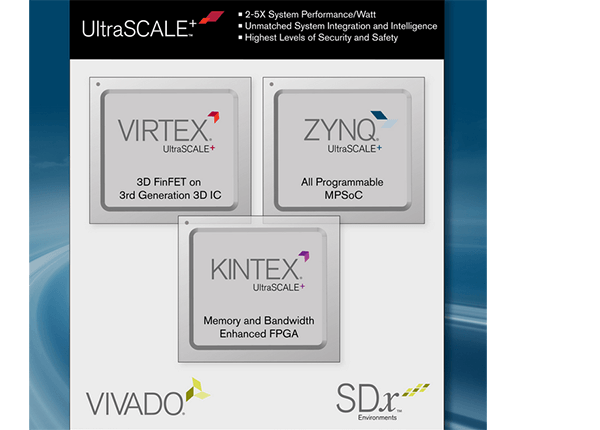

The Virtex UltraScale+ devices join the Zynq UltraScale+ MPSoCs and Kintex UltraScale+ FPGAs showcasing the availability of all three families of the Xilinx 16nm portfolio. The UltraScale+ portfolio provides 2 – 5x greater system-level performance/watt over 28nm devices and is suited for LTE Advanced and early 5G Wireless, Automotive ADAS, Cloud Computing, Industrial Internet-of-Things (IoT), SDN/NFV, and Video/Vision markets.

Xilinx said it is actively engaged with more than one hundred customers on the UltraScale+ portfolio with design tools, and has already shipped devices and/or boards to over sixty of these customers.

“The successful delivery of our Virtex UltraScale+ FPGA marks the availability of all three UltraScale+ 16nm families, which are already providing more than one hundred customers with the ability to develop next generation designs using cutting edge FinFET-based devices, development boards and tools. Our “Three-Peat” execution – with three consecutive generations of leadership technology at 28nm, 20nm, and now at 16nm – showcases our sustained commitment to being first to market with the most advanced products in our industry,” said Victor Peng, executive vice president and general manager of the Programmable Products Group at Xilinx.

Xilinx Outlines its 16nm UltraScale+ Family of FPGAs

Xilinx introduced its next-generation 16nm UltraScale+ family of FPGAs, featuring new memory, 3D-on-3D and multi-processing SoC (MPSoC) technologies.

The UltraScale+ family also includes a new interconnect optimization technology and will leverage TSMC’s 16FF+ FinFET 3D transistors.

Xilinx estimates the UltraScale+ family will deliver 2–5X greater system level performance/watt over 28nm devices. Key applications are expected to include LTE Advanced and early 5G wireless, terabit wired communications, automotive ADAS, and industrial Internet-of-Things (IoT).

Some highlights:

- Memory Enhanced Programmable Devices: UltraRAM attacks one of the largest bottlenecks affecting FPGA- and SoC-based system performance and power by enabling SRAM integration. The new on-chip memory could be used for deep packet and video buffering. UltraRAM scales up to 432 Mbits in a variety of configurations.

- SmartConnect Technology: Interconnect optimization technology for FPGAs. It provides additional 20-30 percent performance, area, and power advantages through intelligent system-wide interconnect optimization. While the UltraScale architecture attacks the silicon-level interconnect bottleneck through re-architected routing, clocking, and logic fabric, SmartConnect applies interconnect topology optimizations to match design-specific throughput and latency requirements while reducing interconnect logic area.

- 3D-on-3D Technology: The high end of the UltraScale+ portfolio leverages the combined power of 3D transistors and third generation of Xilinx 3D ICs. Just as FinFETs enable a non-linear improvement in performance/watt over planar transistors, 3D ICs enable a non-linear improvement in systems integration and bandwidth/watt over monolithic devices.

- Heterogeneous Multi-processing Technology: The new Zynq UltraScale+ MPSoCs include all of the aforementioned FPGA technologies with an unprecedented level of heterogeneous multi-processing, deploying the “the right engines for the right tasks.” These new devices deliver approximately 5X system level performance/watt relative to previous alternatives. At the center of the processing-subsystem is the 64-bit quad-core ARM® Cortex®-A53 processor, capable of hardware virtualization, asymmetric processing, and full ARM TrustZone® technology support.

“Xilinx is delivering a generation ahead of value with 16nm FinFET FPGAs and MPSoCs to a variety of next generation applications,” said Victor Peng, executive vice president and general manager of the Programmable Products Group at Xilinx. “Our new UltraScale+ 16nm portfolio delivers 2-5X higher system performance-per-watt, a dramatic leap in system integration and intelligence, and the highest level of security and safety required by our customers. These capabilities enable Xilinx to significantly expand its available market.”

Early customer engagements are in process for the UltraScale+ families. First tape out and early access release of the design tools are scheduled for the second calendar quarter of 2015.