At Intel “Architecture Day” this week in Santa Clara, California, Intel executives outlined a broad strategy to address “an expanding universe of data-intensive workloads for PCs and other smart consumer devices, high-speed networks, ubiquitous artificial intelligence (AI), specialized cloud data centers and autonomous vehicles.”

Intel’s overall strategy is anchored on six pillars:

Process: Intel expects advanced packaging solutions to enable continued exponential scaling in computing density by extending transistor density to the third dimension.

Architecture: Intel sees a future with a diverse mix of scalar, vector, matrix and spatial architectures deployed in CPU, GPU, accelerator and FPGA sockets, enabled by a scalable software stack, integrated into systems by advanced packaging technology.

Memory: the company believes its is uniquely positioned to combine in-package memory and Intel Optane technology to fill gaps in the memory hierarchy to provide bandwidth closer to the silicon die.

Interconnect: Intel will offer a complete range of leading interconnect products enables the heterogeneous computing landscape at scale. This includes wireless connections for 5G infrastructure as well as silicon-level package and die interconnects.

Security: the company believes it is uniquely positioned to deliver security technologies that help improve the end-to-end and to make security advancements a key differentiator.

Software: Intel will offer a common set of tools that can address Intel silicon for developers. The company says that for every order of magnitude performance potential of a new hardware architecture there are two orders of magnitude performance enabled by software.

Some highlights of Intel Architecture Day:

- Intel demonstrated a range of 10nm-based systems in development for PCs, data centers and networking.

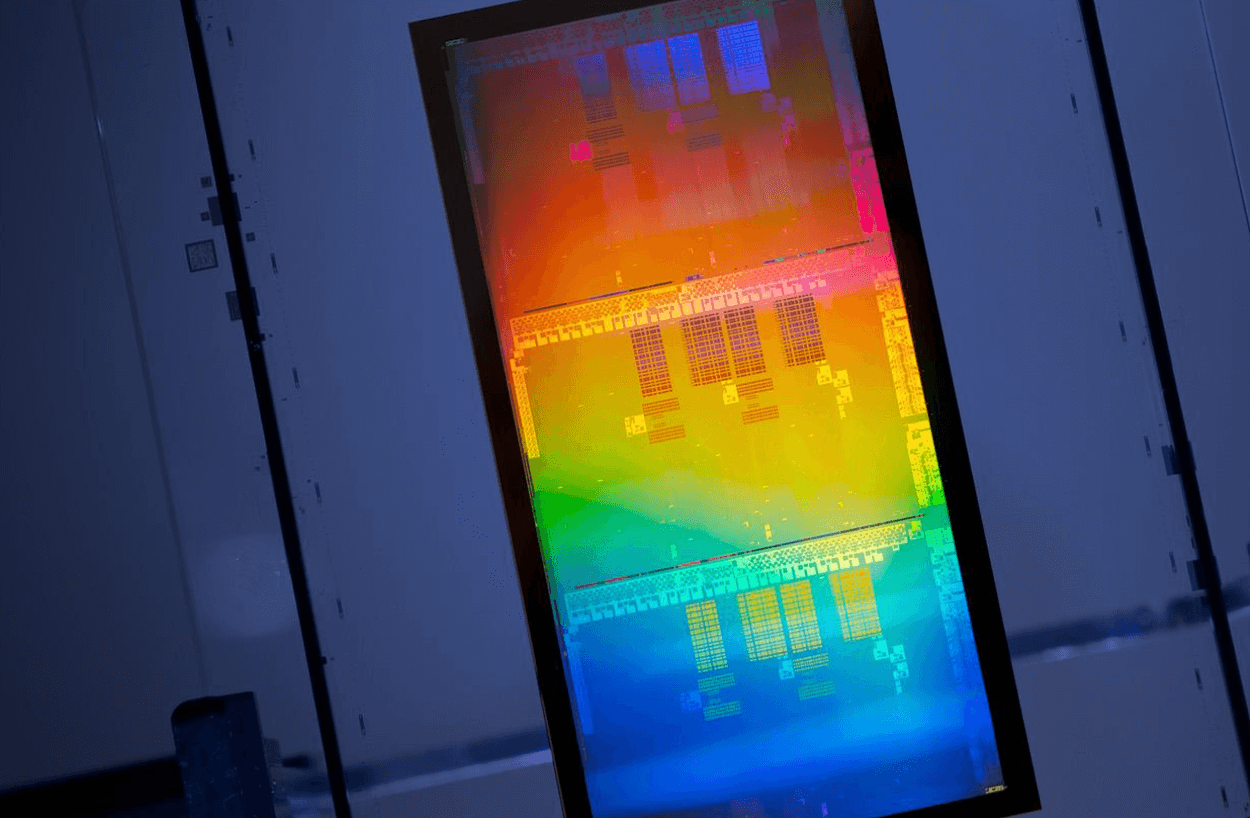

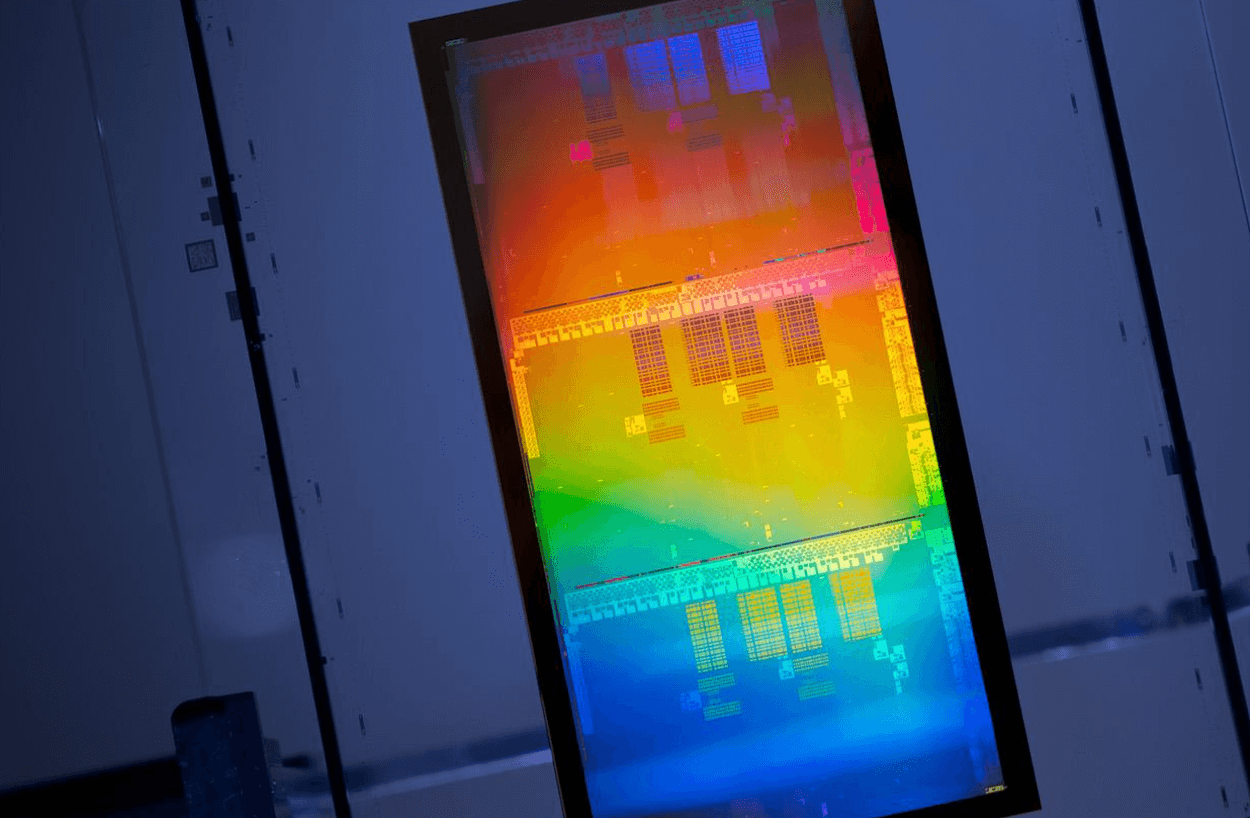

- Foveros: Intel demonstrated a new 3D packaging technology, called “Foveros,” which for the first time brings 3D stacking to logic-on-logic integration.

- Foveros will will allow products to be broken up into smaller “chiplets,” where I/O, SRAM and power delivery circuits can be fabricated in a base die and high-performance logic chiplets are stacked on top.

- Intel expects to launch a range of products using Foveros beginning in the second half of 2019.

- The first Foveros product will combine a high-performance 10nm compute-stacked chiplet with a low-power 22FFL base die.

- Sunny Cove — Intel’s next-generation CPU microarchitecture, increases performance per clock and power efficiency for general purpose computing tasks, and includes new features to accelerate special purpose computing tasks like AI and cryptography.

- Sunny Cove will be the basis for Intel’s next-generation server (Intel Xeon) and client (Intel Core™) processors later next year.

- Next-Generation Graphics: Intel’s Gen11 integrated graphics will offer 64 enhanced execution units, more than double previous Intel Gen9 graphics (24 EUs), breaking the 1 TFLOPS barrier.

- Intel reaffirmed its plan to introduce a discrete graphics processor by 2020.

- “One API” Software: a new 0“One API” project aimes to simplify the programming of diverse computing engines across CPU, GPU, FPGA, AI and other accelerators. The project includes a comprehensive and unified portfolio of developer tools for mapping software to the hardware that can best accelerate the code. A public project release is expected to be available in 2019.

- Memory and Storage: Intel showed how SSDs based on its 1 Terabit QLC NAND die move more bulk data from HDDs to SSDs, allowing faster access to that data.

- Deep Learning Reference Stack: Intel is releasing the Deep Learning Reference Stack, an integrated, highly-performant open source stack optimized for Intel Xeon® Scalable platforms.