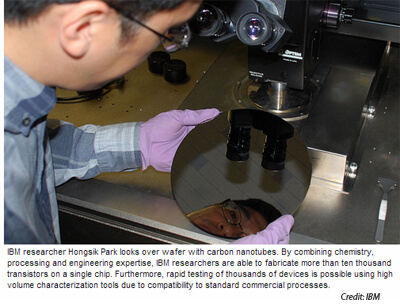

IBM announced a breakthrough in building a semiconductor using carbon nanotubes instead of silicon. IBM researchers created a device consisting of more than ten thousand working transistors made of nano-sized tubes of carbon. Standard semiconductor processes were used to fabricate the device.

IBM has previously demonstrated that carbon nanotube transistors can operate as excellent switches at molecular dimensions of less than ten nanometers – less than half the size of the leading silicon technology.

“Carbon nanotubes, borne out of chemistry, have largely been laboratory curiosities as far as microelectronic applications are concerned. We are attempting the first steps towards a technology by fabricating carbon nanotube transistors within a conventional wafer fabrication infrastructure,” said Supratik Guha, Director of Physical Sciences at IBM Research. “The motivation to work on carbon nanotube transistors is that at extremely small nanoscale dimensions, they outperform transistors made from any other material. However, there are challenges to address such as ultra high purity of the carbon nanotubes and deliberate placement at the nanoscale. We have been making significant strides in both.”

http://www-03.ibm.com/press/us/en/pressrelease/39250.wss

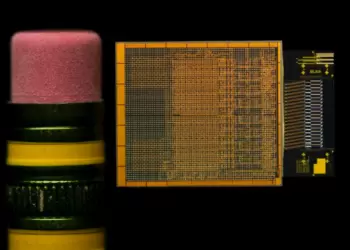

In November 2010, IBM announced significant advances in its path to integrate electrical and optical devices on the same piece of silicon. The new CMOS Integrated Silicon Nanophotonics, which is the result of a decade of development at IBM’s global Research laboratories, promises over 10X improvement in integration density than is feasible with current manufacturing techniques.

At the time, IBM said it anticipates that Silicon Nanophotonics will dramatically increase the speed and performance between chips. In addition to combining electrical and optical devices on a single chip, the new IBM technology can be produced on the front-end of a standard CMOS manufacturing line. Transistors can share the same silicon layer with silicon nanophotonics devices. To make this approach possible, IBM researchers have developed a suite of integrated ultra-compact active and passive silicon nanophotonics devices that are all scaled down to the diffraction limit — the smallest size that dielectric optics can afford. This makes possible the integration of modulators, germanium photodetectors and ultra-compact wavelength-division multiplexers with high-performance analog and digital CMOS circuitry.

“The development of the Silicon Nanophotonics technology brings the vision of on-chip optical interconnections much closer to reality,” said Dr. T.C. Chen, vice president, Science and Technology, IBM Research. “With optical communications embedded into the processor chips, the prospect of building power-efficient computer systems with performance at the Exaflop level is one step closer to reality.”