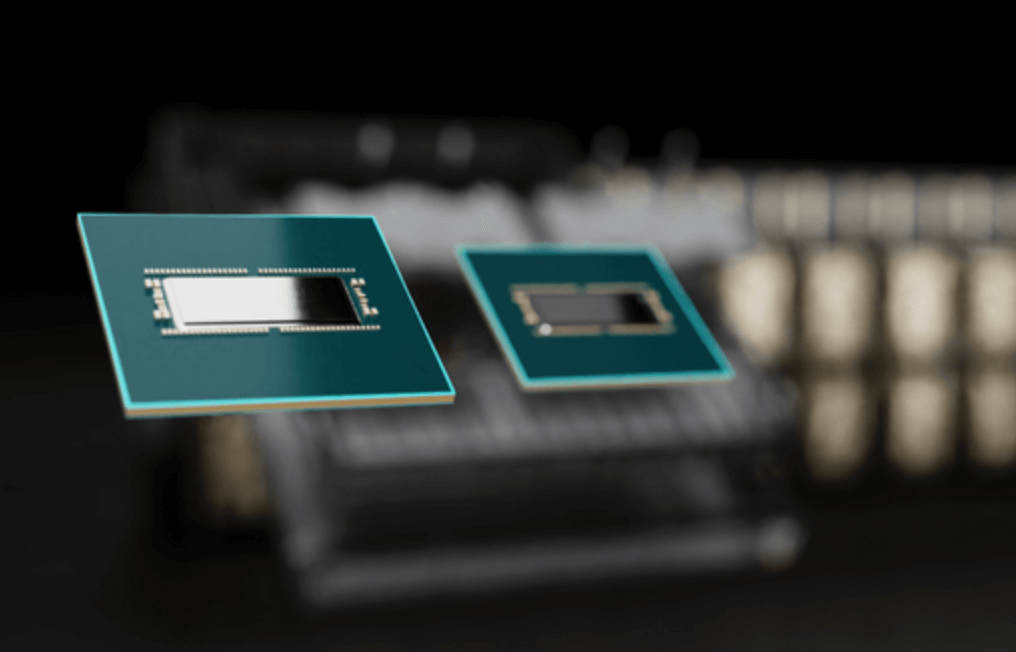

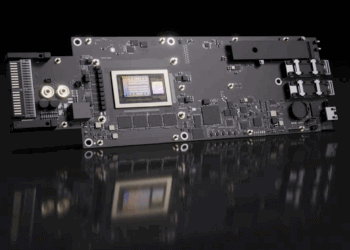

NVIDIA will expand the use of its NVLink chip-to-chip and die-to-die interconnect technology in its GPUs, CPUs, DPUs, NICs and SOCs. The company also plans to open the technolgy to other for for custom chip and chiplet integrations.

NVIDIA NVLink-C2C is built on top of NVIDIA’s world-class SERDES and LINK design technology, and it is extensible from PCB-level integrations and multichip modules to silicon interposer and wafer-level connections, delivering extremely high bandwidth while optimizing for energy and die area efficiency.

In addition to NVLink-C2C, NVIDIA will also support the developing Universal Chiplet Interconnect Express (UCIe) standard. Custom silicon integration with NVIDIA chips can either use the UCIe standard or NVLink-C2C, which is optimized for lower latency, higher bandwidth and greater power efficiency.

Some of NVLink-C2C’s key features include:

● High Bandwidth – supporting high-bandwidth coherent data transfers between processors and accelerators

● Low Latency – supporting atomics between processors and accelerators to perform fast synchronization and high-frequency updates to shared data

● Low Power and High Density – using advanced packaging, it is 25x more energy efficient and 90x more area-efficient than PCIe Gen 5 on NVIDIA chips

● Industry-Standard Support – works with Arm’s AMBA CHI or CXL industry-standard protocols for interoperability between devices

“Chiplets and heterogeneous computing are necessary to counter the slowing of Moore’s law,” said Ian Buck, vice president of Hyperscale Computing at NVIDIA. “We’ve used our world-class expertise in high-speed interconnects to build uniform, open technology that will help our GPUs, DPUs, NICs, CPUs and SoCs create a new class of integrated products

NVIDIA estimates that its NVLink-C2C interconnect could deliver up to 25x more energy efficiency and be 90x more area-efficient than PCIe Gen 5 on NVIDIA chips and enable coherent interconnect bandwidth of 900 Gbps or higher.

“As the future of CPU design is increasingly accelerated and multichip, it is critical to support chiplet-based SoCs across the ecosystem,” said Chris Bergey, senior vice president and general manager of the Infrastructure Line of Business at Arm. “Arm is supporting a broad set of connectivity standards and designing our AMBA CHI protocol to support these future technologies, including collaborating with NVIDIA on NVLink-C2C to address use cases like coherent connectivity between CPUs, GPUs and DPUs.”